Edition 3.0 2022-11 COMMENTED VERSION

# INTERNATIONAL STANDARD

N. C.

Digital addressable lighting interface – Part 101: General requirements – System components

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2022 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Secretariat 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 info@iec.ch www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

#### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee, ...). It also gives information on projects, replaced and withdrawn publications.

IEC Just Published - webstore.iec.ch/justpublished Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

#### IEC Customer Service Centre - webstore.iec.ch/csc If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service Centre: sales@iec.ch.

#### IEC Products & Services Portal - products.iec.ch

Discover our powerful search engine and read freely all the publications previews. With a subscription you will always have access to up to date content tailored to your needs.

#### Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing more than 22 300 terminological entries in English and French, with equivalent terms in 19 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

Edition 3.0 2022-11 COMMENTED VERSION

# **INTERNATIONAL STANDARD**

in non is

Digital addressable lighting interface -Part 101: General requirements – System components

**INTERNATIONAL** ELECTROTECHNICAL COMMISSION

ISBN 978-2-8322-6101-9

ICS 29.140.50; 29.140.99

Warning! Make sure that you obtained this publication from an authorized distributor.

# CONTENTS

| F  | OREWO      | 0RD                                                        | 7  |

|----|------------|------------------------------------------------------------|----|

| IN | TRODU      | JCTION                                                     | 10 |

| 1  | Scop       | e                                                          | 12 |

| 2  | Norm       | native references                                          | 12 |

| 3  |            | as and definitions                                         |    |

| 4  |            | eral                                                       |    |

| -  |            |                                                            |    |

|    | 4.1<br>4.2 | Purpose                                                    |    |

|    | 4.2<br>4.3 | System structure and architecture                          |    |

|    | 4.3        | System information flow                                    |    |

|    | 4.4        | Command types                                              |    |

|    | 4.5        | Bus units                                                  |    |

|    | 4.6.1      |                                                            |    |

|    | 4.6.2      |                                                            |    |

|    | 4.6.3      | 5                                                          |    |

|    | 4.6.4      | -                                                          |    |

|    | 4.6.5      |                                                            |    |

|    | 4.6.6      |                                                            |    |

|    | 4.6.7      |                                                            |    |

|    | 4.7        | Bus power supply and load calculations                     |    |

|    | 4.7.1      |                                                            |    |

|    | 4.7.2      | -                                                          |    |

|    | 4.7.3      |                                                            |    |

|    | 4.8        | Wiring                                                     |    |

|    | 4.8.1      |                                                            |    |

|    | 4.8.2      |                                                            |    |

|    | 4.9        | Electrical safety requirements                             |    |

|    | 4.9.1      |                                                            |    |

|    | 4.9.2      |                                                            |    |

|    | 4.9.3      | Electric strength                                          | 24 |

|    | 4.9.4      | Limitation of the touch current from the device to the bus | 24 |

|    | 4.10       | Earthing of the bus                                        | 25 |

|    | 4.11       | Power interruptions at bus units                           | 25 |

|    | 4.11       | 1 Different levels of power interruptions                  | 25 |

|    | 4.11       | 2 Short power interruptions of external power supply       | 25 |

|    | 4.11       | 3 External power cycle                                     | 26 |

|    | 4.11       | 4 Short interruptions of bus power supply                  | 26 |

|    | 4.11       | 5 Bus power down                                           | 26 |

|    | 4.11       | .6 System start-up timing                                  | 26 |

| 5  | Elect      | rical specification                                        | 28 |

|    | 5.1        | General                                                    | 28 |

|    | 5.2        | Marking of the interface                                   | 28 |

|    | 5.3        | Capacitors between the interface and earth                 | 28 |

|    | 5.4        | Signal voltage rating                                      | 28 |

|    | 5.5        | Signal current rating                                      | 29 |

|   | 5.6   | Marking of bus powered bus unit                 | 29 |

|---|-------|-------------------------------------------------|----|

|   | 5.7   | Signal rise time and fall time                  | 30 |

| 6 | Bus p | power supply                                    | 31 |

|   | 6.1   | General                                         | 31 |

|   | 6.2   | Marking of the bus power supply terminals       | 31 |

|   | 6.3   | Capacitors between the interface and earth      | 31 |

|   | 6.4   | Voltage rating                                  | 31 |

|   | 6.5   | Current rating                                  | 32 |

|   | 6.5.1 | General current rating                          | 32 |

|   | 6.5.2 | Single bus power supply current rating          | 32 |

|   | 6.5.3 | 5 1 11 5 5                                      |    |

|   | 6.5.4 |                                                 |    |

|   | 6.6   | Bus power supply timing requirements            | 34 |

|   | 6.6.1 | Short power supply interruptions                |    |

|   | 6.6.2 |                                                 |    |

| 7 | Trans | smission protocol structure                     |    |

|   | 7.1   | General                                         | 35 |

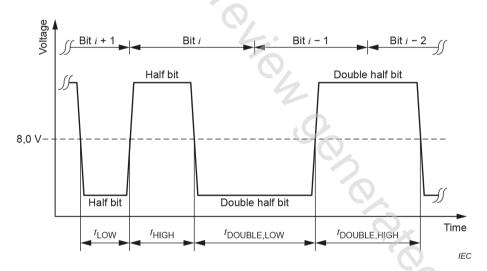

|   | 7.2   | Bit encoding                                    |    |

|   | 7.2.1 | Start bit and data bit encoding                 | 35 |

|   | 7.2.2 | Stop condition encoding                         | 35 |

|   | 7.3   | Frame description                               |    |

|   | 7.4   | Frame types                                     | 36 |

|   | 7.4.1 | 16-bit forward frame                            |    |

|   | 7.4.2 |                                                 |    |

|   | 7.4.3 |                                                 |    |

|   | 7.4.4 |                                                 |    |

|   | 7.4.5 |                                                 |    |

|   | 7.4.6 |                                                 |    |

| 8 | Timir | ng                                              |    |

|   | 8.1   | Single-master transmitter timing                | 37 |

|   | 8.1.1 | Single-master transmitter bit timing            | 37 |

|   | 8.1.2 | Single-master transmitter frame sequence timing | 37 |

|   | 8.2   | Receiver timing                                 | 38 |

|   | 8.2.1 | Receiver bit timing                             | 38 |

|   | 8.2.2 |                                                 | 39 |

|   | 8.2.3 | Receiver frame size violation                   | 40 |

|   | 8.2.4 |                                                 |    |

|   | 8.2.5 | Reception of backward frames                    | 40 |

|   | 8.3   | Multi-master transmitter timing                 | 41 |

|   | 8.3.1 | Multi-master transmitter bit timing             | 41 |

|   | 8.3.2 | Multi-master transmitter frame sequence timing  | 41 |

| 9 | Meth  | od of operation                                 | 42 |

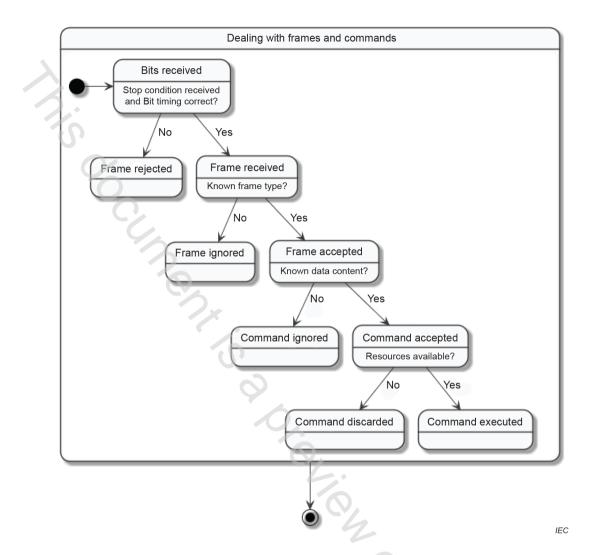

|   | 9.1   | Dealing with frames and commands                | 42 |

|   | 9.1.1 | General                                         |    |

|   | 9.1.2 | Frame received or rejected                      | 43 |

|   | 9.1.3 | Frame accepted or ignored                       | 43 |

|   | 9.1.4 | Command accepted or ignored                     | 43 |

|   | 9.1.5 |                                                 |    |

| 9.2                | Collision avoidance, collision detection and collision recovery | 44      |

|--------------------|-----------------------------------------------------------------|---------|

| 9.2.2              | General                                                         | 44      |

| 9.2.2              | Collision avoidance                                             | 44      |

| 9.2.3              | Collision detection                                             | 44      |

| 9.2.4              | Collision recovery                                              | 46      |

| 9.3                | Transactions                                                    | 47      |

| 9.4                | Send-twice forward frames and send-twice commands               | 47      |

| 9.5                | Command iteration                                               | 48      |

| 9.6                | Usage of a shared interface                                     | 48      |

| 9.6.1              | General                                                         | 48      |

| 9.6.2              | Backward frames                                                 | 49      |

| 9.6.3              | Forward frames                                                  | 49      |

| 9.7                | Use of multiple bus power supplies                              | 49      |

| <del>9.7</del> —   | -Command execution                                              | <u></u> |

| 10 Decl            | aration of variables                                            | 49      |

| 11 Defi            | ition of commands                                               | 49      |

| <del>12—Test</del> | procedures                                                      |         |

|                    | · · · · · · · · · · · · · · · · · · ·                           |         |

| Annex A ( | informative) Background information for systems                         | 50 |

|-----------|-------------------------------------------------------------------------|----|

| A.1       | Wiring information                                                      | 50 |

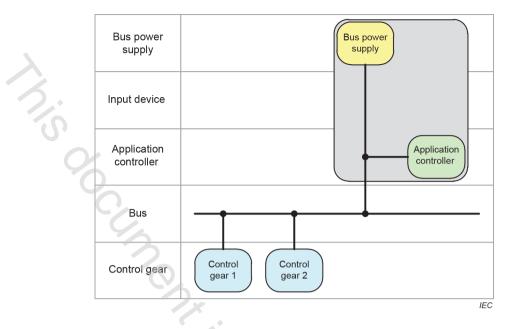

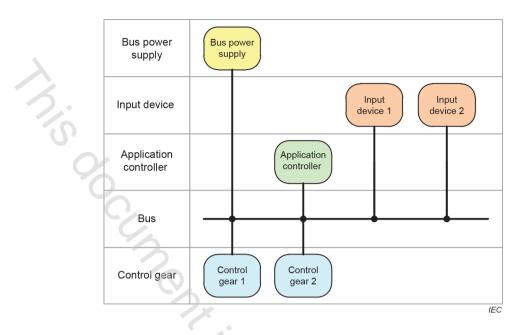

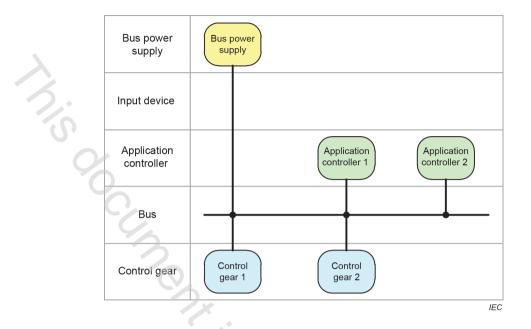

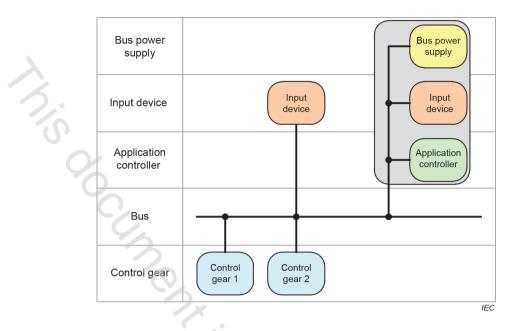

| A.2       | System architectures                                                    | 51 |

| A.2.1     |                                                                         |    |

| A.2.2     | Single-master architecture                                              | 51 |

| A.2.3     | Multi-master architecture with one application controller               | 52 |

| A.2.4     | Multi-master architecture with more than one application controller     | 53 |

| A.2.5     | Multi-master architecture with integrated input device                  | 54 |

| A.2.6     | Multi-master architecture with integrated input device and power supply | 55 |

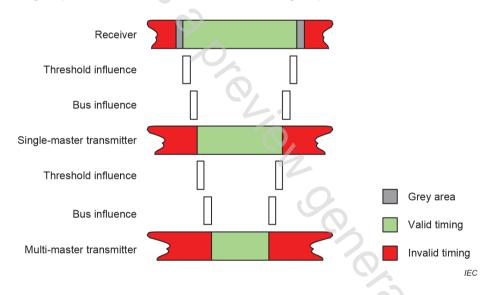

| A.3       | Collision detection                                                     | 56 |

| A.4       | Timing definition explanations                                          |    |

| A.4.1     |                                                                         |    |

| A.4.2     | 5                                                                       |    |

| A.4.3     | 5                                                                       | 57 |

| A.4.4     |                                                                         | 58 |

| A.5       | Maximum current consumption calculation explanation                     | 58 |

| A.5.1     | Single bus power supply                                                 | 58 |

| A.5.2     | Multiple bus power supplies                                             | 59 |

| A.5.3     | Redundant bus power supplies                                            | 60 |

| A.6       | Communication layer overview                                            | 61 |

| A.6.1     | General                                                                 | 61 |

| A.6.2     | Physical layer                                                          | 62 |

| A.6.3     | Data link layer                                                         | 62 |

| A.6.4     | Network layer                                                           | 62 |

| A.6.5     | Transport layer                                                         | 62 |

| A.6.6     | Session layer                                                           | 62 |

| A.6.7     | Presentation layer                                                      | 62 |

| A.6.8     | Application layer                                                       | 62 |

| A.7       | Effects-on of combining version number 1 and version number 2.y devices | 62 |

| Annex B (informative) Touch current                                                                             | 64 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Bibliography                                                                                                    | 65 |

| List of comments                                                                                                | 66 |

|                                                                                                                 |    |

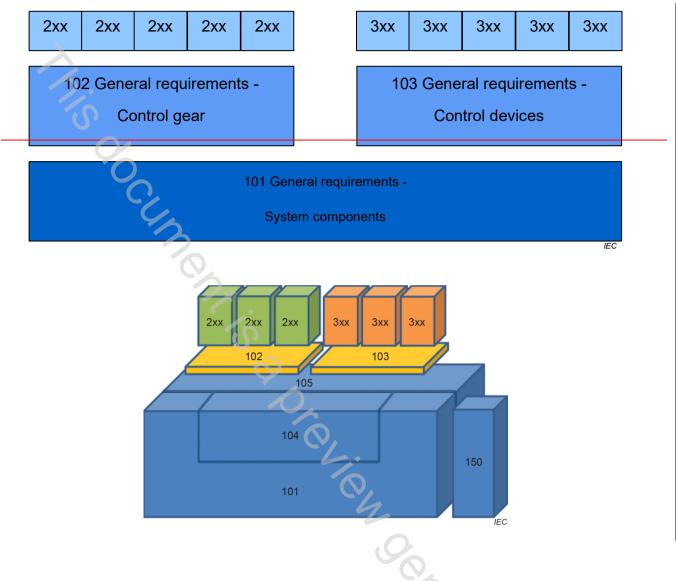

| Figure 1 – IEC 62386 graphical overview                                                                         | 11 |

| Figure 2 – System structure example                                                                             |    |

| Figure 3 – Communication between bus units (example)                                                            |    |

| Figure 4 – Example of a shared interface                                                                        |    |

| Figure 5 – Start-up timing example                                                                              |    |

| Figure 6 – Maximum signal rise and fall time measurements                                                       |    |

| Figure 7 – Minimum signal rise and fall time measurements                                                       |    |

| Figure 8 – Bus power supply current behaviour                                                                   |    |

| Figure 9 – Bus power supply voltage behaviour                                                                   |    |

| Figure 10 – Frame example                                                                                       |    |

| Figure 11 – Bi-phase encoded bits                                                                               |    |

| Figure 12 – Bit timing example                                                                                  |    |

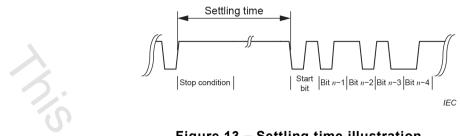

| Figure 13 – Settling time illustration                                                                          |    |

| Figure 14 – Receiver timing decision example                                                                    |    |

| Figure 15 – Dealing with frames and commands                                                                    |    |

| Figure 16 – Collision detection timing decision example                                                         |    |

| Figure 17 – Collision recovery example                                                                          |    |

| Figure A.1 – Single-master architecture example                                                                 |    |

| Figure A.2 – Multi-master architecture example with one application controller                                  | 53 |

| Figure A.3 – Multi-master architecture example with two application controllers                                 | 54 |

| Figure A.4 – Multi-master architecture example with integrated input device                                     | 55 |

| Figure A.5 – Multi-master architecture example with integrated input device and bus                             |    |

| power supply                                                                                                    |    |

| Figure A.6 – Collision detection timing diagram                                                                 |    |

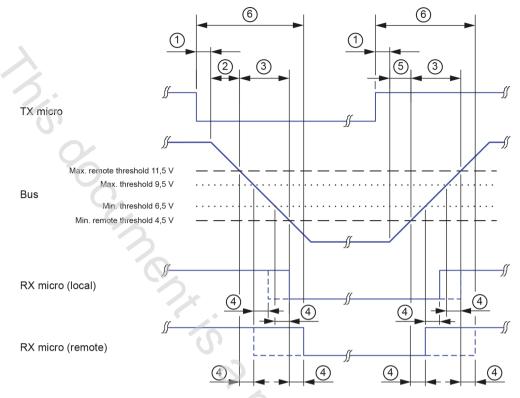

| Figure A.7 – Transmitter and receiver timing illustration                                                       | 58 |

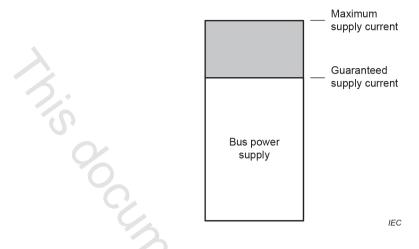

| Figure A.8 – Bus power supply current values                                                                    |    |

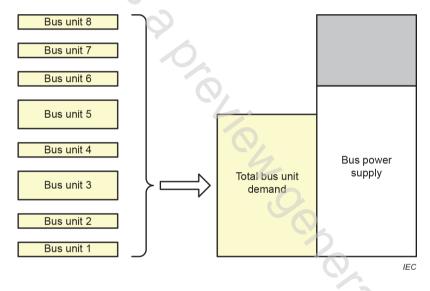

| Figure A.9 – Current demand coverage                                                                            |    |

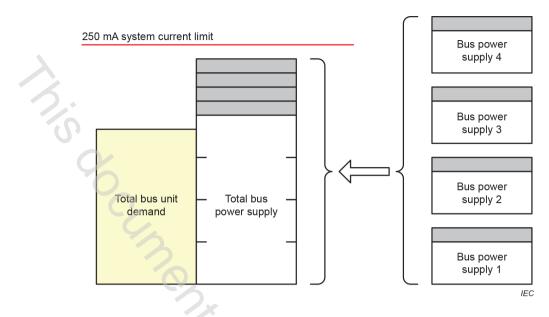

| Figure A.10 – Combination of four bus power supplies                                                            |    |

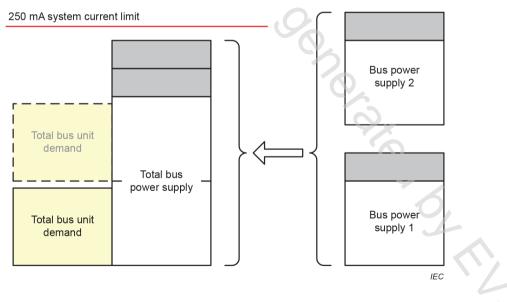

| Figure A.11 – Redundant bus power supplies                                                                      |    |

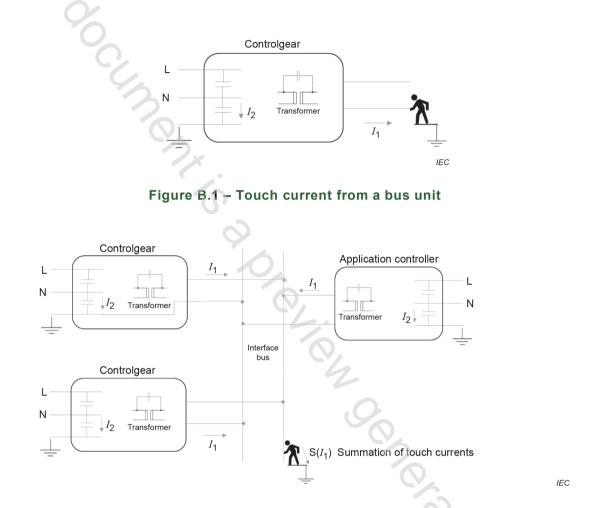

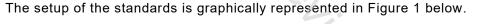

| Figure B.1 – Touch current from a bus unit                                                                      |    |

| Figure B.2 – Summation of touch currents from several bus units                                                 | 64 |

| Table 1 – System components                                                                                     | 10 |

| Table 1 – System components         Table 2 – Transmitters and receivers in bus units                           |    |

| Table 2 – Transmitters and receivers in bus units         Table 3 – Power-interruption timing of external power |    |

| Table 3 – Power-interruption timing of external power         Table 4 – Power-interruption timing of bus power  |    |

| Table 4 – Power-interruption timing of bus power         Table 5 – Short power interruptions                    |    |

| Table 5 – Short power interruptions       Table 6 – Start-up timing                                             |    |

| Table 0 – Start-up tilling       Table 7 – System voltage levels                                                |    |

|                                                                                                                 |    |

| Table 8 – Receiver voltage levels                                                               | 29 |

|-------------------------------------------------------------------------------------------------|----|

| Table 9 – Transmitter voltage levels                                                            | 29 |

| Table 10 – Current rating                                                                       | 29 |

| Table 11 – Signal rise and fall times                                                           | 30 |

| Table 12 – Bus power supply output voltage                                                      | 32 |

| Table 13 – Bus power supply current rating                                                      | 32 |

| Table 14 – Bus power supply dynamic behaviour                                                   | 33 |

| Table 15 – Short circuit timing behaviour                                                       | 34 |

| Table 16 – Transmitter bit timing                                                               | 37 |

| Table 17 – Transmitter settling time values                                                     | 38 |

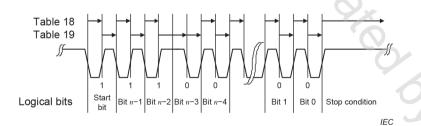

| Table 18 – Receiver timing starting at the beginning of a logical bit                           | 39 |

| Table 19 – Receiver timing starting at an edge inside of a logical bit                          | 39 |

| Table 20 – Receiver settling time values                                                        | 40 |

| Table 21 – Multi-master transmitter bit timing                                                  | 41 |

| Table 22 – Multi-master transmitter settling time values                                        | 42 |

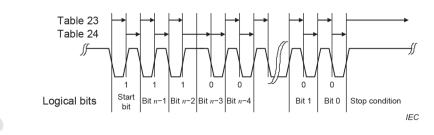

| Table 23 – Checking a logical bit, starting at an edge at the beginning of the bit              | 45 |

| Table 24 – Checking a logical bit, starting at an edge inside the bit                           | 45 |

| Table 25 – Collision recovery timing                                                            | 46 |

| Table 26 – Transmitter command iteration timing                                                 | 48 |

| Table 27 – Receiver command iteration timing                                                    | 48 |

| Table A.1 – Maximum cable length                                                                | 51 |

| Table A.2 – OSI layer model of the IEC 62386 series                                             | 61 |

| Table A.3 – Effects <del> on</del> of combining version number 1 and version number 2.y devices | 63 |

and version number 2.y devices.....

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

# DIGITAL ADDRESSABLE LIGHTING INTERFACE -

# Part 101: General requirements – System components

# FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

This commented version (CMV) of the official standard IEC 62386-101:2022 edition 3.0 allows the user to identify the changes made to the previous IEC 62386-101:2014+ AMD1:2018 CSV edition 2.1. Furthermore, comments from IEC TC 34 experts are provided to explain the reasons of the most relevant changes, or to clarify any part of the content.

A vertical bar appears in the margin wherever a change has been made. Additions are in green text, deletions are in strikethrough red text. Experts' comments are identified by a blue-background number. Mouse over a number to display a pop-up note with the comment.

This publication contains the CMV and the official standard. The full list of comments is available at the end of the CMV.

IEC 62386-101 has been prepared by IEC technical committee 34: Lighting. It is an International Standard.

This third edition cancels and replaces the second edition published in 2014 and Amendment 1:2018. This edition constitutes a technical revision.

This edition includes the following significant technical changes with respect to the previous edition:

- a) the scope has been updated;

- b) safety and earthing have been updated and extended;

- c) references have been updated;

- d) the use of bus-power and external-power has been clarified;

- e) polarity sensitivity for bus units including a bus power supply has been updated;

- f) frame sizes of 32 bits are no longer reserved.

The text of this International Standard is based on the following documents:

| Draft       | Report on voting |

|-------------|------------------|

| 34/947/FDIS | 34/988/RVD       |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at www.iec.ch/members\_experts/refdocs. The main document types developed by IEC are described in greater detail at www.iec.ch/standardsdev/publications.

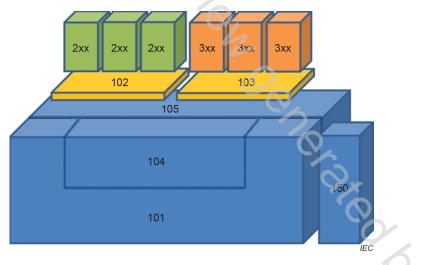

This Part 101 of IEC 62386 is intended to be used in conjunction with:

- Part 102, which contains general requirements for the relevant product type (control gear), and with the appropriate Part 2xx (particular requirements for control gear);

- Part 103, which contains general requirements for the relevant product type (control devices), and the appropriate Part 3xx (particular requirements for control devices);

- Part 104, which contains general requirements for wireless and alternative wired system components;

- Part 105, which contains particular requirements for firmware transfer for control gear and control devices.

A list of all parts in the IEC 62386 series, published under the general title *Digital addressable lighting interface*, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under webstore.iec.ch in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IMPORTANT - The "colour inside" logo on the cover page of this document indicates that it netor contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

# INTRODUCTION

IEC 62386 contains several parts, referred to as series. The IEC 62386 series specifies a bus system for control by digital signals of electronic lighting equipment. The IEC 62386-1xx series includes the basic specifications. Part 101 contains general requirements for system components, Part 102 extends this information with general requirements for control gear and Part 103 extends it further with general requirements for control devices. Parts 104 and 105 can be applied to control gear or control devices. Part 104 gives requirements for wireless and alternative wired system components. Part 105 describes firmware transfer. Part 150 gives requirements for an auxiliary power supply which can be stand-alone, or built into control gear or control devices.

The IEC 62386-2xx series extends the general requirements for control gear with lamp specific extensions (mainly for backward compatibility with Edition 1 of IEC 62386) and with control gear specific features.

The IEC 62386-3xx series extends the general requirements for control devices with input device specific extensions describing the instance types as well as some common features that can be combined with multiple instance types.

This second third edition of IEC 62386-101 is intended to be used in conjunction with IEC 62386-102:2014 and IEC 62386-102:2014/AMD1:— and with the various parts that make up the IEC 62386-2xx series for control gear, together with IEC 62386-103:2014 and IEC 62386-103:2014/AMD1— and the various parts that make up the IEC 62386-3xx series of particular requirements for control devices. The division into separately published parts provides for ease of future amendments and revisions. Additional requirements will be added as and when a need for them is recognized.

The setup of the standards is graphically represented in Figure 1 below.

# IEC 62386-101:2022 CMV © IEC 2022 - 11 -

Figure 1 – IEC 62386 graphical overview 1

When this part of IEC 62386 refers to any of the clauses of the other<u>two</u> parts of the IEC 62386-1xx series, the extent to which such a clause is applicable and the order in which the tests are to be performed are is specified. The other parts also include additional requirements, as necessary.

All numbers used in this document are decimal numbers unless otherwise noted. Hexadecimal numbers are given in the format 0xVV, where VV is the value. Binary numbers are given in the format XXXXXXX b or in the format XXXX XXXX, where X is 0 or 1, "x" in binary numbers means "don't care".

# DIGITAL ADDRESSABLE LIGHTING INTERFACE -

# Part 101: General requirements – System components

# 1 Scope

This part of IEC 62386 is applicable to system components in a bus system for control by digital signals of electronic lighting equipment which is in line with the requirements of IEC 61347 (all parts), with the addition of DC supplies.

NOTE Tests in this standard are type tests. Requirements for testing individual bus units during production are not included.

The control methods, algorithms and data exchange methods of application controllers used for lighting control are not within the scope of the IEC 62386 series. EMC requirements are not within the scope of the IEC 62386 series. **2**

# 2 Normative references 3

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61347-1:2015, Lamp controlgear – Part 1: General and safety requirements IEC 61347-1:2015/AMD1:2017

IEC 62386-102:<del>2014</del>2022, Digital addressable lighting interface – Part 102: General requirements – Control gear <u>IEC 62386-102:2014/AMD1:</u><sup>4</sup>

IEC 62386-103:<del>2014</del>2022, Digital addressable lighting interface – Part 103: General requirements – Control devices <u>IEC 62386-103:2014/AMD1:</u><sup>2</sup>

IEC 62386-104, Digital addressable lighting interface – Part 104: General requirements – Wireless and alternative wired system components

IEC 62386-105, Digital addressable lighting interface – Part 105: Particular requirements for control gear and control devices – Firmware Transfer

IEC 62386-2xx (all parts), Digital addressable lighting interface – Part 2xx: Particular requirements for control gear

IEC 62386-3xx (all parts), Digital addressable lighting interface – Part 3xx: Particular requirements for control devices

<sup>&</sup>lt;sup>1</sup>—Under preparation. Stage at the time of publication: IEC DECFDIS 62386-102/AMD1:2018.

<sup>&</sup>lt;sup>2</sup> Under preparation. Stage at the time of publication: IEC RFDIS 62386-103/AMD1:2018.

IEC 62386-101-2022 CMV © IEC 2022 - 13 -

IEC 61000-4-11, Electromagnetic compatibility (EMC) – Part 4-11:Testing and measurement techniques - Voltage dips, short interruptions and voltage variations immunity tests for equipment with input current up to 16 A per phase

IEC 60664-1, Insulation coordination for equipment within low-voltage supply systems -Part 1: Principles, requirements and tests

IEC 60990:2016, Methods of measurement of touch current and protective conductor current

IEC 61643-11 Low-voltage surge protective devices - Part 11: Surge protective devices connected to low-voltage power systems – Requirements and test methods

#### Terms and definitions 3

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminology databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

# 3.1

# active state

phase of low level voltage during a transmission

Note 1 to entry: Noise and short pulses may be ignored and therefore do not change the state.

# 3.2

# advanced bus power supply

bus power supply capable of checking the bus for fault conditions before switching on its output continuously

Note 1 to entry: Examples of fault conditions are mains voltage connected to the bus or short circuit of the bus.

# 3.3

# application controller

control device that is connected to the bus and sends commands in order to control input devices and/or control gear connected to the same bus .0 02 11 7

# 3.4

# backward frame

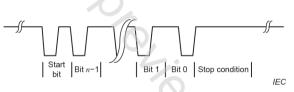

frame used for backward transmission

# 3.5

# backward transmission

transmission of data as a reply to and triggered by a forward transmission

# 3.6

#### bus

two-wire connection line carrying power and frames

# 3.7

# bus powered

drawing the power for operation from the bus

#### bus power down

bus power interruption longer than 45 ms

# 3.9

# bus power interruption

abnormal condition where the bus voltage is in the receiver low level voltage range, but not because of a transmitter being active

# 3.10

bus power supply unit feeding defined energy to the bus

# 3.11

bus unit

logical unit or combination of logical units, containing one transmitter and optionally one receiver

Note 1 to entry: See 4.6.6.

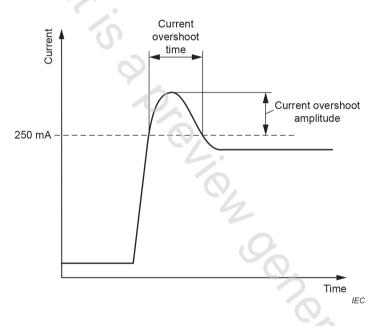

# 3.12

# charge overshoot

product of current overshoot time and current overshoot amplitude

Note 1 to entry: Within this standard the charge overshoot is a simple multiplication of the current overshoot time and the current overshoot amplitude.

# 3.13

# collision

situation in which two or more transmitters are transmitting simultaneously

Note 1 to entry: Collisions can go unnoticed if the transmission timing is sufficiently similar and the transmitted frame content is identical.

# 3.14

#### command

forward transmission with appropriate information content, intended to cause a reaction in the receiver

Note 1 to entry: A receiver, having decoded a command can, when appropriate, decide to ignore the command.

Note 2 to entry: Refer to IEC 62386-102, IEC 62386-103, IEC 62386-104, IEC 62386-105, the IEC 62386-2xx series and IEC 62386-3xx series for command definitions.

# 3.15

#### control device

device that is connected to the bus and sends commands to other devices (for example control gear) connected to the same bus

Note 1 to entry: Control devices can also receive commands and backward transmissions. Control devices can contain application controllers and/or input devices.

# 3.16

# control gear

device that is connected to the bus and receives commands in order to control at least one output in a direct or indirect way

Note 1 to entry: The lamp controlgear described in IEC 61347-1 can cover control gear.

#### current overshoot time

time per bit during which the current supplied by the bus power supply is above the allowed maximum of 250 mA after a transition from idle state to active state

Note 1 to entry: See 6.5.4.

#### 3.18

#### destroy area

time slot where a valid frame cannot be guaranteed and therefore the frame has to be invalidated ensured

# 3.19

#### edge

change from active state to idle state or vice versa

# 3.20

# event message

command sent by a control device in order to distribute information on the bus

# 3.21

# externally powered

drawing the power for operation from a separate power supply

Note 1 to entry: The separate power supply can be mains power, DC power, etc.

# 3.22

forward frame frame used for forward transmission

# 3.23

# forward frame priority

property of a forward frame used to prioritize access to the bus

# 3.24

#### forward transmission

transmission of data initiated by a control device

Note 1 to entry: See also 3.5.

# 3.25

#### frame

set of consecutive bits followed by a stop condition

Note 1 to entry: See Clause 8 for the timing definition of a stop condition.

# 3.26

#### grey area

time slot containing the decision point separating adjacent time slots

Note 1 to entry: A grey area indicates that the decision is arbitrary. Typically the previous or next entry in a table should be used as an action. See Clause 8 for further information.

# 3.27

#### idle state

phase of high level voltage between and during transmissions

Note 1 to entry: Noise and short pulses may be ignored and therefore do not change the state.

# input device

control device that is connected to the bus and sends commands using a multi-master transmitter in order to distribute information about user actions and/or sensor values

Note 1 to entry: Input devices do not transmit commands to the control gear.

# 3.29

#### instance

signal processing unit of an input device

# 3.30

instruction

command transmitted to change one or more variables in a bus unit 4

# 3.31

# integrated bus power supply

bus power supply integrated into a physical device also containing a bus unit

# 3.32

#### interface

terminals or wires for connection to the bus

# 3.33

#### logical unit

control gear or control device that conforms to IEC 62386-102 or IEC 62386-103

Note 1 to entry: See 4.6.6.

# 3.34

# multi-master application controller

application controller that is <u>intended to share</u> capable of sharing **5** the bus with other control devices and uses a multi-master transmitter

# 3.35

# multi-master transmitter

transmitter that follows the multi-master timing and supports collision detection, collision avoidance, and collision recovery methods

Note 1 to entry: Multi-master transmitters are used in control devices intended for multi-master control systems.

# 3.36

# proprietary forward frame

frame other than a standard forward frame, reserved forward frame or backward frame

Note 1 to entry: Proprietary frames are intended for manufacturer-specific purposes

forward frame for manufacturer-specific purposes

# 3.37

#### query

command transmitted to observe a variable in a bus unit

Note 1 to entry: A query can be followed by a backward frame.

# 3.38

#### receiver

part of a bus unit detecting and decoding frames on the bus

# reserved

intended for future use by this standard

# 3.40

# send-twice command

command transmitted by send-twice forward frames

Note 1 to entry: Refer to 9.4, IEC 62386-102, IEC 62386-103, the IEC 62386-2xx series and IEC 62386-3xx series for further details on send-twice commands.

# 3.41

# send-twice forward frame

forward frame that needs to be transmitted twice with a limited settling time in order to be processed by the receiver

# 3.42

#### settling time

time during which the bus is in idle state after the last rising edge of one frame and before the first falling edge of the next frame

# 3.43

# single-master application controller

application controller that is intended not to share the bus with other control devices not required to use a multi-master transmitter **6**

Note 1 to entry: The implication is that no other application controllers, and no other input devices with event messages enabled, may be connected to the bus.

# 3.44

# standard forward frame

forward frame as defined and described in the IEC 62386 series

# 3.45

#### system failure

bus power interruption longer than 550 ms

# 3.46

#### transaction

uninterruptible set of one or more consecutive forward frames transmitted from a single control device, with zero or more backward frames

# 3.47

#### transmitter

part of a bus unit placing frames on the bus

# 3.48

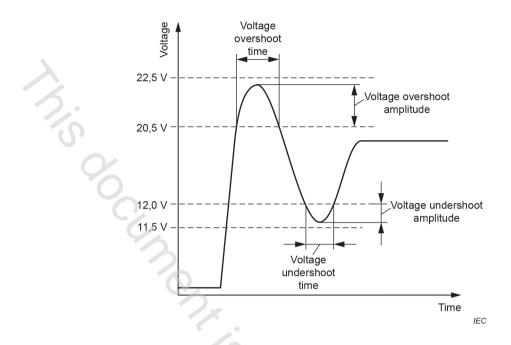

#### voltage overshoot time

time per bit during which the voltage supplied by the bus power supply is above 20,5 V after a transition from active state to idle state

Note 1 to entry: See 6.5.4.

# 3.49

# voltage undershoot time

time per bit during which the voltage supplied by the bus power supply is below 12,0 V after a transition from active state to idle state

Note 1 to entry: See 6.5.4.

#### frame accepted

frame that has been received and uses the correct frame type and data bit content

# 3.51

#### frame ignored

frame received but not accepted

# 3.52

#### frame received

frame with a valid start bit, valid data bits, and a stop condition

# 3.53

frame rejected frame not received

#### 3.54 FELV

# functional extra-low voltage

ELV in a circuit provided for functional purposes and not fulfilling the requirements for SELV (or PELV)

Note 1 to entry: FELV has basic insulation from LV.

Note 2 to entry: An FELV circuit is not safe to touch.

[SOURCE: IEC 60598-1:2020, 1.2.42.1, modified – The notes have been added.]

# 4 General

# 4.1 Purpose

The standardization of the digital addressable lighting interface is intended to achieve interoperable multi-vendor operation below the level of building management systems.

EN 50491 and ISO 14672 are not applicable for the purposes of this standard.

Annex A gives further information for systems.

NOTE The IEC 63044 series and ISO/IEC 14762 are not applicable for the purposes of this IEC 62386 series. The IEC 63044 series can be applicable to application controllers if intended to be used as HBES/BACS.

# 4.2 Version number

The version shall be in the format "x.y", where the major version number x is in the range of 0 to 62 and the minor version number y is in the range of 0 to 2. When the version number is encoded into a byte, the major version number x shall be placed in bits 7 to 2 and the minor version number y shall be placed in bits 1 to 0.

At each amendment to an edition of IEC 62386-101 the minor version number shall be incremented by one.

At a new edition of IEC 62386-101 the major version number shall be incremented by one and the minor version number shall be set to 0.

The current version number is "2.01" "3.0".

**NOTE** Normally 2 amendments on IEC documents are made before a new edition is created. IEC documents are generally subject to two amendments before a new edition is prepared.

IEC 62386-101:2022 CMV © IEC 2022 - 19 -

# 4.3 System structure and architecture

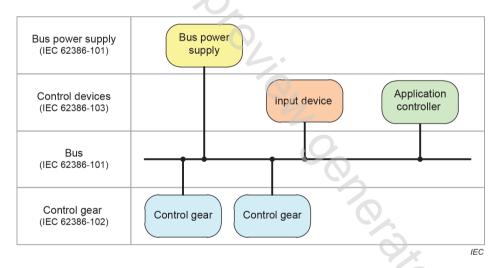

A system conformant to this standard shall consist of the components listed in Table 1.

| Component              | Quantity | For detailed information see                                    |

|------------------------|----------|-----------------------------------------------------------------|

| Bus power supply       | ≥ 1      | Clause 6                                                        |

| Control gear           | ≥ 0      | IEC 62386-102 <del>:2014 and<br/>IEC 62386-102:2014/AMD1:</del> |

| Application controller | ≥ 1      | IEC 62386-103 <del>:2014 and</del><br>IEC 62386-103:2014/AMD1:  |

| Input devices          | ≥ 0      | IEC 62386-103 <del>:2014 and</del><br>IEC 62386-103:2014/AMD1:  |

| Bus                    | 1        | Subclause 4.8 and Clause A.2                                    |

# Table 1 – System components

In a system all bus units as well as the bus power supplies are connected in parallel to the bus.

NOTE As a consequence of this, every frame is visible to all power supplies, control gear, and control devices on the bus.

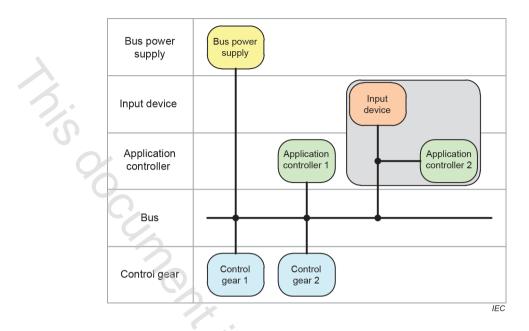

Figure 2 shows a system structure example.

Figure 2 – System structure example

See 4.8 for detailed information on the wiring and Clause A.2 for information on possible system architectures.

# 4.4 System information flow

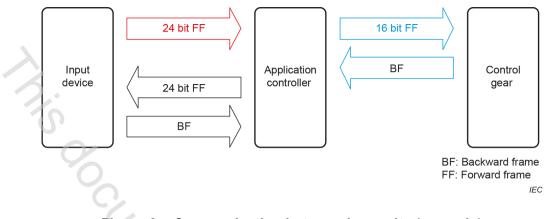

Figure 3 shows the different frame types that are used for communication between the bus units in a system. A backward frame is only ever transmitted in response to a forward frame.

– 20 – IEC 62386-101:2022 CMV © IEC 2022

Figure 3 – Communication between bus units (example)

A direct information flow from an input device to control gear is not allowed. In addition to communications shown in Figure 3, for firmware transfer (IEC 62386-105), application controllers can transmit 32-bit forward frames and all three of the bus units shown can receive 32-bit forward frames. Multi-master application controllers can also be transmitters of 8-bit backward frames. **7**

NOTE An example of a system conforming to this document can consist of an application controller and control gear only, see A.2.4. In such a system, user input does not result in 24-bit forward frames on the bus.

# 4.5 Command types

Bus units conforming to this document shall use the following different types of commands for communication:

- event messages,

- instructions, and

- queries.

NOTE Refer to the other parts of the IEC 62386 series for further details on event messages, instructions and queries.

# 4.6 Bus units

#### 4.6.1 Transmitters and receivers in bus units

Table 2 gives a short summary of the different receivers and transmitters allowed for each bus unit. It is not allowed for a bus unit to transmit or receive other frames than the ones indicated in Table 2, except proprietary forward frames. See 7.4 for details of the different frame types.

| Bus unit                                                                                                                                                            | Receiver of                        | Transmitter of                                                                |                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------|

| Control goor                                                                                                                                                        | 32-bit forward frames <b>8</b>     | Backward frames, following the single-master timing requirements <sup>a</sup> |                                                |

| Control gear                                                                                                                                                        | 16-bit forward frames              |                                                                               |                                                |

| Input device                                                                                                                                                        | 32-bit forward frames              | 24-bit forward frames                                                         |                                                |

| Input device                                                                                                                                                        | 24-bit forward frames              | Backward frames <sup>a</sup>                                                  |                                                |

| 0                                                                                                                                                                   | 32-bit forward frames              | 32-bit forward frames                                                         | Following the multi-master timing requirements |

| Multi-master application                                                                                                                                            | 24-bit forward frames              | 24-bit forward frames                                                         |                                                |

| controller                                                                                                                                                          | 16-bit forward frames <sup>b</sup> | 16-bit forward frames                                                         |                                                |

|                                                                                                                                                                     | Backward frames                    | Backward frames <sup>a</sup>                                                  |                                                |

| Single-master application<br>controller         Backward frames <sup>c</sup> 16-bit forward frames, following the single<br>master timing requirements <sup>d</sup> |                                    |                                                                               |                                                |

| <sup>a</sup> No collision detection or collision avoidance methods shall be applied to backward frame transmissions.                                                |                                    |                                                                               |                                                |

Table 2 – Transmitters and receivers in bus units

Only applicable when the multi-master application controller is able to process 16-bit forward frames transmitted by other application controllers.

С Only required if the single-master application controller uses addressing or queries.

A single-master application controller can also send 24-bit frames if polling input devices, and 32-bit forward frames.

#### 4.6.2 **Control gear**

A control gear shall be conformant to this document and to IEC 62386-102 and the applicable parts of the IEC 62386-2xx series.

It shall contain a receiver for 16-bit forward frames and a transmitter for transmitting backward frames. The backward frame transmitter shall conform to the timing requirements for a single-master transmitter defined in 8.1 and shall not implement collision detection or recovery. It can contain a receiver for 32-bit forward frames.

#### 4.6.3 Input device

An input device shall be conformant to this document and to IEC 62386-103 and the applicable parts of the IEC 62386-3xx series.

It shall contain a multi-master transmitter following the multi-master transmitter timing requirements defined in 8.3 to transmit 24-bit forward frames. It shall also contain a transmitter to transmit backward frames. The backward frame transmitter shall conform to the timing requirements for a single-multi-master transmitter and shall not implement collision detection or recovery.

NOTE Although they are logically distinct objects, the multi-master transmitter and the backward frame transmitter can share the same hardware.

An input device shall contain a receiver to receive 24-bit forward frames transmitted by other control devices. It can contain a receiver for 32-bit forward frames.

#### 4.6.4 Single-master application controller

A single-master application controller shall be conformant to this document and to IEC 62386-103.

It shall contain a transmitter following the transmitter timing requirements defined in 8.1 to transmit forward frames.

NOTE-4 Typically, however, a single-master application controller also contains a receiver to receive backward frames transmitted by control gear.

A single-master application controller shall use the commands defined in IEC 62386-102 and, if applicable, the relevant parts of the IEC 62386-2xx series to communicate with the control gear.

NOTE 2 The control methods and algorithms of an application controller used for lighting control are not in the scope of IEC 62386.

# 4.6.5 Multi-master application controller

A multi-master application controller shall be conformant to this document and to IEC 62386-103.

It shall contain a multi-master transmitter following the multi-master transmitter timing requirements defined in 8.3 to transmit forward frames. It shall also contain a transmitter to transmit backward frames. The backward frame transmitter shall conform to the timing requirements for a multi-master transmitter and shall not implement collision detection or recovery **9**. It shall contain a receiver to receive backward frames as well as forward frames transmitted by other control devices. It can contain a receiver for 32-bit forward frames. It shall not transmit backward frames in response to 16-bit forward frames.

A multi-master application controller shall use the commands defined in IEC 62386-102 and, if applicable, the relevant parts of the IEC 62386-2xx series to communicate with the control gear. It shall use the commands defined in IEC 62386-103 and, if applicable, the relevant parts of the IEC 62386-3xx series to communicate with control devices. If applicable, a multi-master application controller shall use the commands defined in IEC 62386-105 to achieve firmware transfer to control gear and control devices.

NOTE-4 A multi-master application controller can also receive and process 16-bit forward frames transmitted by other application controllers and/or react to queries.

NOTE 2 The control methods and algorithms of an application controller used for lighting control are not in the scope of IEC 62386.

NOTE 3 The standardisation of data exchange between different application controllers sharing the same bus is not in the scope of IEC 62386.

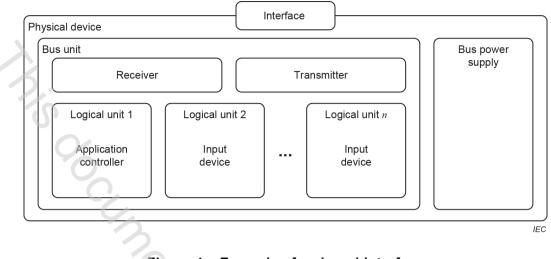

#### 4.6.6 Sharing an interface

More than one logical unit may share one physical interface. Figure 4 shows an example where n logical units and a bus power supply share the physical interface.

# IEC 62386-101:2022 CMV © IEC 2022 - 23 -

Figure 4 – Example of a shared interface

An application controller may be built into a bus unit which also contains an input device, with both the application controller and the input device sharing the same physical interface. A bus unit of that kind shall support a command to deactivate the application controller, thus enabling the bus unit to be used in the same way as if it contained only the input device.

# 4.6.7 Power for operation 10

Bus units shall be solely bus powered or solely externally powered, or meet one of the following two cases:

- The bus unit is configurable between bus powered and externally powered, where the configuration shall not be automatic based upon the presence or absence of the supply, and the bus unit meets the following conditions:

- connection or removal of the external supply or bus power supply shall not cause operation to change between bus powered and externally powered, and

- it meets the requirements for bus powered bus units when configured as bus powered, and meets the requirements for externally powered bus units when configured as externally powered, and

- changing the configured power source does not change any functionality that is described in any part of the IEC 62386 series, except due to requirements that differ between bus powered and externally powered bus units.

- The bus unit is bus powered, uses an external supply only for behaviour not specified in any part of the IEC 62386 series, and meets the requirements in the implemented parts of the IEC 62386 series with the external supply disconnected.

NOTE 1 An example of a bus unit that is configurable between bus powered and externally powered is a sensor which can draw a relatively high current when bus powered, limiting the number of such devices that can be connected to the bus, or can be configured to be externally powered and so allow more devices on the bus.

NOTE 2 An example of a bus unit that is bus powered, but uses an external supply only for behaviour not specified in any part of the IEC 62386 series, is a bus powered push-button panel with a backlight, where the backlight operates only when an external supply is connected.

NOTE 3 An example of a bus unit that does not meet these requirements is bus powered LED control gear, requiring a second device to provide power for the LEDs, where the second device is externally powered. Another example is a bus powered pulse width modulation (PWM) dimmer which requires an external 24 V DC supply to drive its output – the dimmer can instead be externally powered from the 24 V DC supply.

# 4.7 Bus power supply and load calculations

# 4.7.1 Current demand coverage

In one system the sum of all bus units' current consumption when not transmitting (see 5.5, Table 10) shall not exceed the sum of all bus supplies' guaranteed supply current (see 6.5.1, Table 13). See also Clause A.5.

Additional current is needed during transmission to drive dynamic processes such as charging capacitances within the system.

$\sum I_{\text{Bus Unit}} + I_{\text{Dynamic Processes}} \leq \sum I_{\text{Power Supply Guaranteed}}$

There is no universally valid equation for calculating the current needed for dynamic processes since this current depends on the system wiring and system structure.

# 4.7.2 Maximum signal current compliance

The sum of all bus power supplies' maximum supply current connected to the bus shall never exceed 250 mA.

$$\sum I_{Power Supply Guaranteed} \leq \sum I_{Power Supply Maximum} \leq 250 \text{ mA}$$

# 4.7.3 Simplified system calculation

For a system consisting of just one bus power supply, bus powered bus units, and *n* externally powered bus units, for example control gear, the following simplification is recommended:

$$2 \text{ mA} \times n_{\text{Externally Powered Bus Units}} + \sum I_{\text{Bus Powered Bus Units}} \leq \frac{I_{\text{Power Supply Guaranteed}}}{1.2}$$

The factor 1,2 is a ballpark figure and an approximation that takes an additional current of 20 % needed for dynamic processes into account.

# 4.8 Wiring

# 4.8.1 Wiring structure

The bus wiring should be connected in a star topology, a linear topology or a mixture of both. The wiring shall not be done in a ring structure. The two leads which serve as the bus shall be located in the same cable or cable conduit. In the cable or cable conduit the two leads shall be next to each other in order to prevent unintended coupling to other signals.

NOTE Depending on local installation directives and insulation requirements the two wires can be located in the same cable as the mains power supply leads.

# 4.8.2 Wiring specification

Apart from transient effects during transmission, at all times during the operation of the system, the voltage across the interface of any device shall not differ by more than 2,0 V from the voltage across the interface of each and every other device connected to the bus. See also Clause A.1 for further details.

NOTE 1 The voltage drop depends on the sum of the supply currents of all power supplies, the specific resistance of the leads and the wiring length.

NOTE 2 This requirement can limit the total wiring length in the system.

IEC 62386-101:2022 CMV © IEC 2022 - 25 -

# 4.9 Electrical safety requirements 11

# 4.9.1 General

This Subclause 4.9 describes the additional safety requirements for the implementation of digital addressable lighting interface, in addition to the product safety requirements given in the relevant product safety standard.

# 4.9.2 Insulation

The minimum requirement for system components conformant to this standard shall be basic insulation as defined in IEC 61347-1.

The bus wiring and the interface shall be considered a FELV circuit or network.

NOTE 1 This means that systems other than FELV are not covered by this document.

The interface shall have at least basic insulation as required for at least 230 V AC mains, or the product working voltage, whichever is higher, according to IEC 60664-1.

NOTE 2 This voltage level is applicable to e.g. the basic insulation between the interface circuit and mains or the supplementary insulation between the bus wiring and touchable conductive parts of the user interface.

If the working voltage exceeds 230 V AC (RMS), and this working voltage can be applied on the interface in the case of a single fault condition, then there shall be a warning included in the manual, also recommended to be marked on the product, indicating that the working voltage is higher than 230 V AC (RMS).

NOTE 3 Working voltage is defined in IEV 581-21-19. This is not usually the mains voltage.

The insulation between the mains and the interface shall be designed for the applicable overvoltage category (OVC), as defined in IEC 60664-1, and shall not be less than OVC II.

NOTE 4 If bus wiring is likely, when installed, to be subjected to impulse voltages that exceed OVC II, then additional measures to be provided to the bus can be considered, for example impulse voltage protection or use of products designed for higher OVC. This can be related to bus wiring being partly outdoors.

# 4.9.3 Electric strength

The requirements of IEC 61347-1:2015, Clause 12 apply, replacing the term "lamp controlgear" with the term "bus unit".

The value used for working voltage shall be at least 230 V AC, or the product working voltage, whichever is higher.

The over voltage protective device (SPD) shall be disconnected if it complies with IEC 61643-11, when conducting the insulation and electric strength test.

# 4.9.4 Limitation of the touch current from the device to the bus

The touch current shall be limited to 0,5 mA RMS.

The touch current shall be measured with the measuring network described in IEC 60990:2016, Figure 4.

The value of the touch current shall be made available in the product documentation by the manufacturer of the product.

Annex B gives further information on touch current.

NOTE The use of the term "touch current" does not indicate that the interface is accessible to touch.

# 4.10 Earthing of the bus

The requirement for system components conformant to this standard shall be as defined in IEC 61347-1.

The interface terminals shall not be connected to earth, except in the following situations:

- a device containing a bus power supply having a maximum supply current of 250 mA, where the negative interface terminal is permitted to be connected to earth;

- through a capacitor connected to earth as described in 5.3 or 6.3. 12

NOTE Unexpected currents, caused by multiple connections of the circuit to protective earth, could cause fire in the bus wiring. Earthing could also break the safety requirements for certain luminaires.

#### 4.11 Power interruptions at bus units

#### 4.11.1 Different levels of power interruptions

Table 3 and Table 4 show the different levels of power interruptions at bus units.

| Minimum                  | Typical | Maximum | Description                                               |

|--------------------------|---------|---------|-----------------------------------------------------------|

|                          |         | 200 ms  | Short interruptions of external power supply <sup>a</sup> |

| > 200 ms                 |         | < 5 s   | Grey area                                                 |

| 5 s                      |         |         | External power cycle <sup>b</sup>                         |

| <sup>a</sup> See 4.1     | 1.2.    |         |                                                           |

| <sup>b</sup> See 4.11.3. |         |         |                                                           |

|                          |         |         | U                                                         |

#### Table 3 – Power-interruption timing of external power

Table 4 – Power-interruption timing of bus power

| Minimum                  | Typical | Maximum  | Description                                          |

|--------------------------|---------|----------|------------------------------------------------------|

|                          |         | 40 ms    | Short interruptions of bus power supply <sup>a</sup> |

| > 40 ms                  |         | < 45 ms  | Grey area                                            |

| 45 ms                    |         |          | Bus power down <sup>b</sup>                          |

| > 450 ms                 |         | < 550 ms | Grey area for system failure                         |

| 550 ms                   |         |          | System failure <sup>b</sup>                          |

| <sup>a</sup> See 4.1     | 1.4.    |          | <u> </u>                                             |

| <sup>b</sup> See 4.11.5. |         |          | (                                                    |

#### 4.11.2 Short power interruptions of external power supply

The requirements of 4.11 are applicable for bus units in steady state without communication on the bus.

NOTE 1 Steady state implies for example that the device has finished its power-up and is ready for the intended operation without any changes of the output in progress.

Functional tests for short power interruptions shall be done with test methods and test equipment according to IEC 61000-4-11 at the minimum specified power supply voltage, with test voltage levels given in Table 5. For AC supply the voltage shift shall occur at zero crossing.

|                                  | Test levels |

|----------------------------------|-------------|

| Test voltage level 1             | 70 %        |

| Test voltage level 2             | 0 %         |

| Number of periods with AC supply | 10          |

| Interruption time with DC supply | 200 ms      |

#### Table 5 – Short power interruptions

During the power supply interruption, a change of the state may occur. After the power supply interruption, the bus unit shall be in, or shall re-establish within 30 min, the same state as before the interruption.

NOTE 2 The 30 min time limit is chosen to allow for the long re-ignition time of certain lamp types.

# 4.11.3 External power cycle

After an external power cycle (see Table 3), an externally powered bus unit shall apply poweron behaviour to all logical units simultaneously. During an external power cycle, a bus unit might can possibly still respond to commands.

NOTE The power-on behaviour is defined in IEC 62386-102 and IEC 62386-103.

# 4.11.4 Short interruptions of bus power supply

Bus units shall not interpret short bus power interruptions of up to 40 ms as power down.

NOTE This implies that short bus power interruptions will not trigger power-on behaviour.

Tests for the short interruption of the bus power supply shall be done at the minimum bus power supply voltage.

# 4.11.5 Bus power down

A bus powered bus unit may interpret bus power down as an external power cycle (see 4.11.1). It shall interpret system failure as an external power cycle. The external power cycle and corresponding power-on **13** behaviour shall apply to all logical units simultaneously. See Table 4.

NOTE The power-on behaviour is defined in IEC 62386-102 and IEC 62386-103.

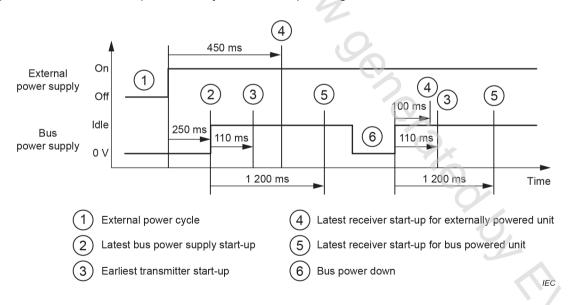

# 4.11.6 System start-up timing

After external power-on, a bus power supply shall be able to supply the guaranteed supply current given in Table 13 after the bus power supply start-up time specified in Table 6 at the latest.

A receiver shall be ready to receive frames within the maximum receiver start-up time specified in Table 6.

A transmitter or a multi-master transmitter shall not start transmissions earlier than the transmitter start-up time specified in Table 6.

| Minimum             | Typical             | Maximum             | Condition                                                                                                                                                                                |

|---------------------|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                     | 250 ms              |                                                                                                                                                                                          |

|                     |                     | 400 ms              | Guaranteed supply current                                                                                                                                                                |

|                     |                     | 400 ms <sup>a</sup> | reached                                                                                                                                                                                  |

|                     |                     | 5 s <sup>b</sup>    |                                                                                                                                                                                          |

|                     |                     | 450 ms <sup>e</sup> |                                                                                                                                                                                          |

|                     |                     | 100 ms              |                                                                                                                                                                                          |

|                     |                     | 1 200 ms            | U = 10 V <sup>d</sup>                                                                                                                                                                    |

| 110 ms <sup>c</sup> |                     |                     |                                                                                                                                                                                          |

| 110 ms              |                     |                     |                                                                                                                                                                                          |

|                     | 110 ms <sup>c</sup> | 110 ms °            | 110 ms       250 ms         250 ms       400 ms         400 ms       400 ms         400 ms       5 s b         450 ms       450 ms         100 ms       1200 ms         110 ms c       5 |

Table 6 – Start-up timing

<sup>a</sup> Applicable if other bus power supplies are allowed in the system.

<sup>b</sup> Applicable if no other bus power supplies are allowed in the system.

<sup>c</sup> Not applicable for transmitters of bus units which cannot determine the bus state.

<sup>d</sup> Idle state, bus voltage measured at the interface of the bus unit.

<sup>e</sup> If an external power cycle occurred and the bus power is not available within 350 ms, the 100 ms timing is applicable.

Figure 5 shows an example of the system start-up timing.

NOTE It follows from the provisions of 4.11.6 that a transmitter could be transmitting before all receivers are ready to receive.

IEC 62386-101:2022 CMV © IEC 2022 - 29 -

# 5 Electrical specification

# 5.1 General

All voltages and currents refer to the interface of the bus unit.

The control interface shall be polarity insensitive, except when a bus power supply is integrated. If the integrated bus power supply is switchable **14**, polarity sensitivity is permitted for both states of the bus power supply (enabled and disabled).

Overvoltage protection is optional, but recommended for the highest rated voltage of the system. If overvoltage protection is not included, it is recommended that the design ensures safe operation in case mains voltage is applied to the interface.

# 5.2 Marking of the interface

The interface shall be marked with "da" or "DA" (for data) on the bus unit. If colour coding is used, the colours representing the "da" or "DA" shall be given on the bus unit.

If there is more than one interface, additional marking shall be used to enable the interfaces to be distinguished from one another.

# 5.3 Capacitors between the interface and earth

If capacitors are connected between the interface circuit and any other part of the device, such as earth, these shall be connected from the negative side of the rectified interface signal. Such capacitors shall fulfil the insulation requirements given in 4.9.

NOTE The capacitance seen on the bus is affected by the capacitance to earth where a capacitor connected between the negative side of the interface and earth on one bus unit is used with another bus unit containing a capacitor connected between the positive side of the interface and earth.

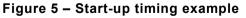

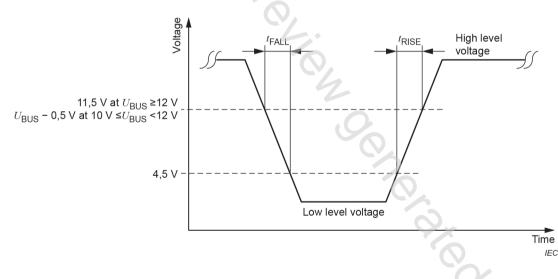

# 5.4 Signal voltage rating

The voltage levels in the system during normal operation shall always be in the range of the nominal system voltage given in Table 7. All bus units as well as the bus power supplies shall withstand the absolute maximum system voltage given in Table 7. Testing shall be done with a current of maximum 260 mA for a duration of 1 s.

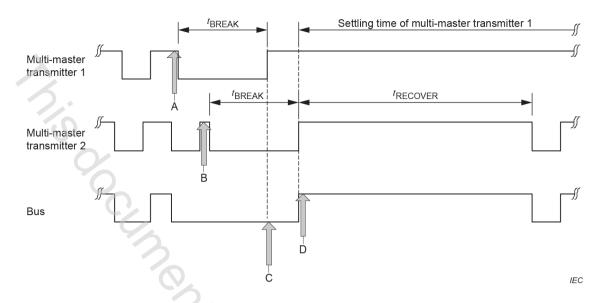

NOTE 1 Voltages outside the nominal system voltage range-might could occur, as a result of ringing on the bus, for example.